JFET

This article needs additional citations for verification. (September 2015) |

Electric current from source to drain in a p-channel JFET is restricted when a voltage is applied to the gate. | |

| Type | Active |

|---|---|

| Pin configuration | drain, gate, source |

| Electronic symbol | |

| |

The junction field-effect transistor (JFET) is one of the simplest types of field-effect transistor.[1] JFETs are three-terminal semiconductor devices that can be used as electronically controlled switches or resistors, or to build amplifiers.

Unlike bipolar junction transistors, JFETs are exclusively voltage-controlled in that they do not need a biasing current. Electric charge flows through a semiconducting channel between source and drain terminals. By applying a reverse bias voltage to a gate terminal, the channel is pinched, so that the electric current is impeded or switched off completely. A JFET is usually conducting when there is zero voltage between its gate and source terminals. If a potential difference of the proper polarity is applied between its gate and source terminals, the JFET will be more resistive to current flow, which means less current would flow in the channel between the source and drain terminals.

JFETs are sometimes referred to as depletion-mode devices, as they rely on the principle of a depletion region, which is devoid of majority charge carriers. The depletion region has to be closed to enable current to flow.

JFETs can have an n-type or p-type channel. In the n-type, if the voltage applied to the gate is negative with respect to the source, the current will be reduced (similarly in the p-type, if the voltage applied to the gate is positive with respect to the source). Because a JFET in a common source or common drain configuration has a large input impedance[2] (sometimes on the order of 1010 ohms), little current is drawn from circuits used as input to the gate.

History

[edit]A succession of FET-like devices was patented by Julius Lilienfeld in the 1920s and 1930s. However, materials science and fabrication technology would require decades of advances before FETs could actually be manufactured.

JFET was first patented by Heinrich Welker in 1945.[3] During the 1940s, researchers John Bardeen, Walter Houser Brattain, and William Shockley were trying to build a FET, but failed in their repeated attempts. They discovered the point-contact transistor in the course of trying to diagnose the reasons for their failures. Following Shockley's theoretical treatment on JFET in 1952, a working practical JFET was made in 1953 by George C. Dacey and Ian M. Ross.[4] Japanese engineers Jun-ichi Nishizawa and Y. Watanabe applied for a patent for a similar device in 1950 termed static induction transistor (SIT). The SIT is a type of JFET with a short channel.[4]

High-speed, high-voltage switching with JFETs became technically feasible following the commercial introduction of Silicon carbide (SiC) wide-bandgap devices in 2008. Due to early difficulties in manufacturing — in particular, inconsistencies and low yield — SiC JFETs remained a niche product at first, with correspondingly high costs. By 2018, these manufacturing issues had been mostly resolved. By then, SiC JFETs were also commonly used in conjunction with conventional low-voltage Silicon MOSFETs.[5] In this combination, SiC JFET + Si MOSFET devices have the advantages of wide band-gap devices as well as the easy gate drive of MOSFETs.[5]

Structure

[edit]The JFET is a long channel of semiconductor material, doped to contain an abundance of positive charge carriers or holes (p-type), or of negative carriers or electrons (n-type). Ohmic contacts at each end form the source (S) and the drain (D). A pn-junction is formed on one or both sides of the channel, or surrounding it using a region with doping opposite to that of the channel, and biased using an ohmic gate contact (G).

Functions

[edit]

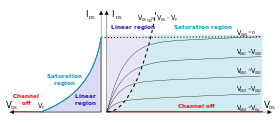

JFET operation can be compared to that of a garden hose. The flow of water through a hose can be controlled by squeezing it to reduce the cross section and the flow of electric charge through a JFET is controlled by constricting the current-carrying channel. The current also depends on the electric field between source and drain (analogous to the difference in pressure on either end of the hose). This current dependency is not supported by the characteristics shown in the diagram above a certain applied voltage. This is the saturation region, and the JFET is normally operated in this constant-current region where device current is virtually unaffected by drain-source voltage. The JFET shares this constant-current characteristic with junction transistors and with thermionic tube (valve) tetrodes and pentodes.

Constriction of the conducting channel is accomplished using the field effect: a voltage between the gate and the source is applied to reverse bias the gate-source pn-junction, thereby widening the depletion layer of this junction (see top figure), encroaching upon the conducting channel and restricting its cross-sectional area. The depletion layer is so-called because it is depleted of mobile carriers and so is electrically non-conducting for practical purposes.[6]

When the depletion layer spans the width of the conduction channel, pinch-off is achieved and drain-to-source conduction stops. Pinch-off occurs at a particular reverse bias (VGS) of the gate–source junction. The pinch-off voltage (Vp) (also known as threshold voltage[7][8] or cut-off voltage[9][10][11]) varies considerably, even among devices of the same type. For example, VGS(off) for the Temic J202 device varies from −0.8 V to −4 V.[12] Typical values vary from −0.3 V to −10 V. (Confusingly, the term pinch-off voltage is also used to refer to the VDS value that separates the linear and saturation regions.[10][11])

To switch off an n-channel device requires a negative gate–source voltage (VGS). Conversely, to switch off a p-channel device requires positive VGS.

In normal operation, the electric field developed by the gate blocks source–drain conduction to some extent.

Some JFET devices are symmetrical with respect to the source and drain.

Schematic symbols

[edit]

The JFET gate is sometimes drawn in the middle of the channel (instead of at the drain or source electrode as in these examples). This symmetry suggests that "drain" and "source" are interchangeable, so the symbol should be used only for those JFETs where they are indeed interchangeable.

The symbol may be drawn inside a circle (representing the envelope of a discrete device) if the enclosure is important to circuit function, such as dual matched components in the same package.[13]

In every case the arrow head shows the polarity of the P–N junction formed between the channel and the gate. As with an ordinary diode, the arrow points from P to N, the direction of conventional current when forward-biased. An English mnemonic is that the arrow of an N-channel device "points in".

Comparison with other transistors

[edit]At room temperature, JFET gate current (the reverse leakage of the gate-to-channel junction) is comparable to that of a MOSFET (which has insulating oxide between gate and channel), but much less than the base current of a bipolar junction transistor. The JFET has higher gain (transconductance) than the MOSFET, as well as lower flicker noise, and is therefore used in some low-noise, high input-impedance op-amps. Additionally the JFET is less susceptible to damage from static charge buildup.[14]

Mathematical model

[edit]Linear ohmic region

[edit]The current in N-JFET due to a small voltage VDS (that is, in the linear or ohmic[15] or triode region[7]) is given by treating the channel as a rectangular bar of material of electrical conductivity :[16]

where

- ID = drain–source current,

- b = channel thickness for a given gate voltage,

- W = channel width,

- L = channel length,

- q = electron charge = 1.6×10−19 C,

- μn = electron mobility,

- Nd = n-type doping (donor) concentration,

- VP = pinch-off voltage.

Then the drain current in the linear region can be approximated as

In terms of , the drain current can be expressed as[citation needed]

Constant-current region

[edit]The drain current in the saturation or active[17][7] or pinch-off region[18] is often approximated in terms of gate bias as[16]

where IDSS is the saturation current at zero gate–source voltage, i.e. the maximum current that can flow through the FET from drain to source at any (permissible) drain-to-source voltage (see, e. g., the I–V characteristics diagram above).

In the saturation region, the JFET drain current is most significantly affected by the gate–source voltage and barely affected by the drain–source voltage.

If the channel doping is uniform, such that the depletion region thickness will grow in proportion to the square root of the absolute value of the gate–source voltage, then the channel thickness b can be expressed in terms of the zero-bias channel thickness a as[19][failed verification]

where

- VP is the pinch-off voltage – the gate–source voltage at which the channel thickness goes to zero,

- a is the channel thickness at zero gate–source voltage.

Transconductance

[edit]The transconductance for the junction FET is given by

where is the pinchoff voltage, and IDSS is the maximum drain current. This is also called or (for transadmittance).[20]

See also

[edit]References

[edit]- ^ Hall, John. "Discrete JFET" (PDF). linearsystems.com. Archived (PDF) from the original on 2022-10-09.

- ^ "Junction Field Effect Transistor". Electronics Tutorials. Archived from the original on 2022-01-31. Retrieved 2022-06-19.

- ^ Grundmann, Marius (2010). The Physics of Semiconductors. Springer-Verlag. ISBN 978-3-642-13884-3.

- ^ a b Junction Field-Effect Devices, Semiconductor Devices for Power Conditioning, 1982.

- ^ a b Flaherty, Nick (October 18, 2018), "Third generation SiC JFET adds 1200 V and 650 V options", EeNews Power Management.

- ^ For a discussion of JFET structure and operation, see for example D. Chattopadhyay (2006). "§13.2 Junction field-effect transistor (JFET)". Electronics (fundamentals and applications). New Age International. pp. 269 ff. ISBN 978-8122417807.

- ^ a b c "Junction Field Effect Transistor (JFET)" (PDF). ETEE3212 Lecture Notes. Archived (PDF) from the original on 2022-10-09.

value of vGS ... for which the channel is completely depleted ... is called the threshold, or pinch-off, voltage and occurs at vGS = VGS(OFF). ... This linear region of operation is called ohmic (or sometimes triode) ... Beyond the knee of the ohmic region, the curves become essentially flat in the active (or saturation) region of operation.

- ^ Sedra, Adel S.; Smith, Kenneth C. "5.11 THE JUNCTION FIELD-EFFECT TRANSISTOR (JFET)" (PDF). Microelectronic Circuits. Archived (PDF) from the original on 2022-10-09.

At this value of vGS the channel is completely depleted ... For JFETs the threshold voltage is called the pinch-off voltage and is denoted VP.

- ^ Horowitz, Paul; Hill, Winfield (1989). The art of electronics (2nd ed.). Cambridge [England]: Cambridge University Press. p. 120. ISBN 0-521-37095-7. OCLC 19125711.

For JFETs the gate-source voltage at which drain current approaches zero is called the "gate-source cutoff voltage", VGS(OFF), or the "pinch-off voltage", VP ... For enhancement-mode MOSFETs the analogous quantity is the "threshold voltage"

- ^ a b Mehta, V. K.; Mehta, Rohit (2008). "19 Field Effect Transistors" (PDF). Principles of electronics (11th ed.). S. Chand. pp. 513–514. ISBN 978-8121924504. OCLC 741256429. Archived (PDF) from the original on 2022-10-09.

Pinch off Voltage (VP). It is the minimum drain–source voltage at which the drain current essentially becomes constant. ... Gate–source cut off voltage VGS (off). It is the gate–source voltage where the channel is completely cut off and the drain current becomes zero.

- ^ a b U. A. Bakshi; Atul P. Godse (2008). Electronics Engineering. Technical Publications. p. 10. ISBN 978-81-8431-503-5.

Do not confuse cutoff with pinch off. The pinch-off voltage VP is the value of the VDS at which the drain current reaches a constant value for a given value of VGS. ... The cutoff voltage VGS(off) is the value of VGS at which the drain current is 0.

- ^ "J201 data sheet" (PDF). Archived (PDF) from the original on 2022-10-09. Retrieved 2021-01-22.

- ^ "A4.11 Envelope or Enclosure". ANSI Y32.2-1975 (PDF). Archived (PDF) from the original on 2022-10-09.

The envelope or enclosure symbol may be omitted from a symbol referencing this paragraph, where confusion would not result

- ^ Kopp, Emilie (2019-01-16). "What's the difference between a MOSFET and a JFET?". Power Electronic Tips. Archived from the original on 2021-05-17. Retrieved 2022-06-16.

- ^ "What is the Ohmic Region of a FET Transistor". www.learningaboutelectronics.com. Retrieved 2020-12-13.

ohmic region ... also called the linear region

- ^ a b Balbir Kumar and Shail B. Jain (2013). Electronic Devices and Circuits. PHI Learning Pvt. Ltd. pp. 342–345. ISBN 9788120348448.

- ^ "Junction Field Effect Transistor". Electronics Tutorials.

Saturation or Active Region

- ^ Scholberg, Kate (2017-03-23). "What is the meaning of "pinch-off region"?".

The "pinch-off region" (or "saturation region") refers to operation of a FET with more than a few volts.

- ^ Storr, Wayne (2013-09-03). "Junction Field Effect Transistor or JFET Tutorial". Basic Electronics Tutorials. Retrieved 2022-10-07.

- ^ Kirt Blattenberger RF Cafe. "JFETS: How They Work, How to Use Them, May 1969 Radio-Electronics". Retrieved 2021-01-04.

yfs – Small-signal, common-source, forward transadmittance (sometimes called gfs-transconductance)

External links

[edit] Media related to JFET at Wikimedia Commons

Media related to JFET at Wikimedia Commons- Physics 111 Laboratory -- JFET Circuits I

- Interactive Explanation of n-channel JFET